业界距离面向桌面与服务器平台的下一代 DDR6 内存标准已不再遥远,存储芯片厂商正与 JEDEC 合作推进相关规范的制定工作。据韩国媒体 The Elec 报道,SK 海力士、三星、镁光等主要存储厂商已在实验室启动 DDR6 设计,并逐步与基板厂商协调模组开发方案。上述协同研发在 JEDEC 这一行业标准组织的主导之下展开,以确保新一代内存在设计层面拥有统一的技术基础。

据悉,早在 2024 年起,相关厂商就可以接触到 JEDEC 给出的首版 DDR6 标准草案,但其中在电压范围、信号定义、功耗封装以及引脚布局等关键参数上仍未最终敲定。随着近期产业界推进力度加大,这些空白预计将逐步被填补,标准定案进程也将随之提速。此前几家头部厂商实际上已经走出样品阶段,转入更为严格的验证周期,为后续量产铺路。

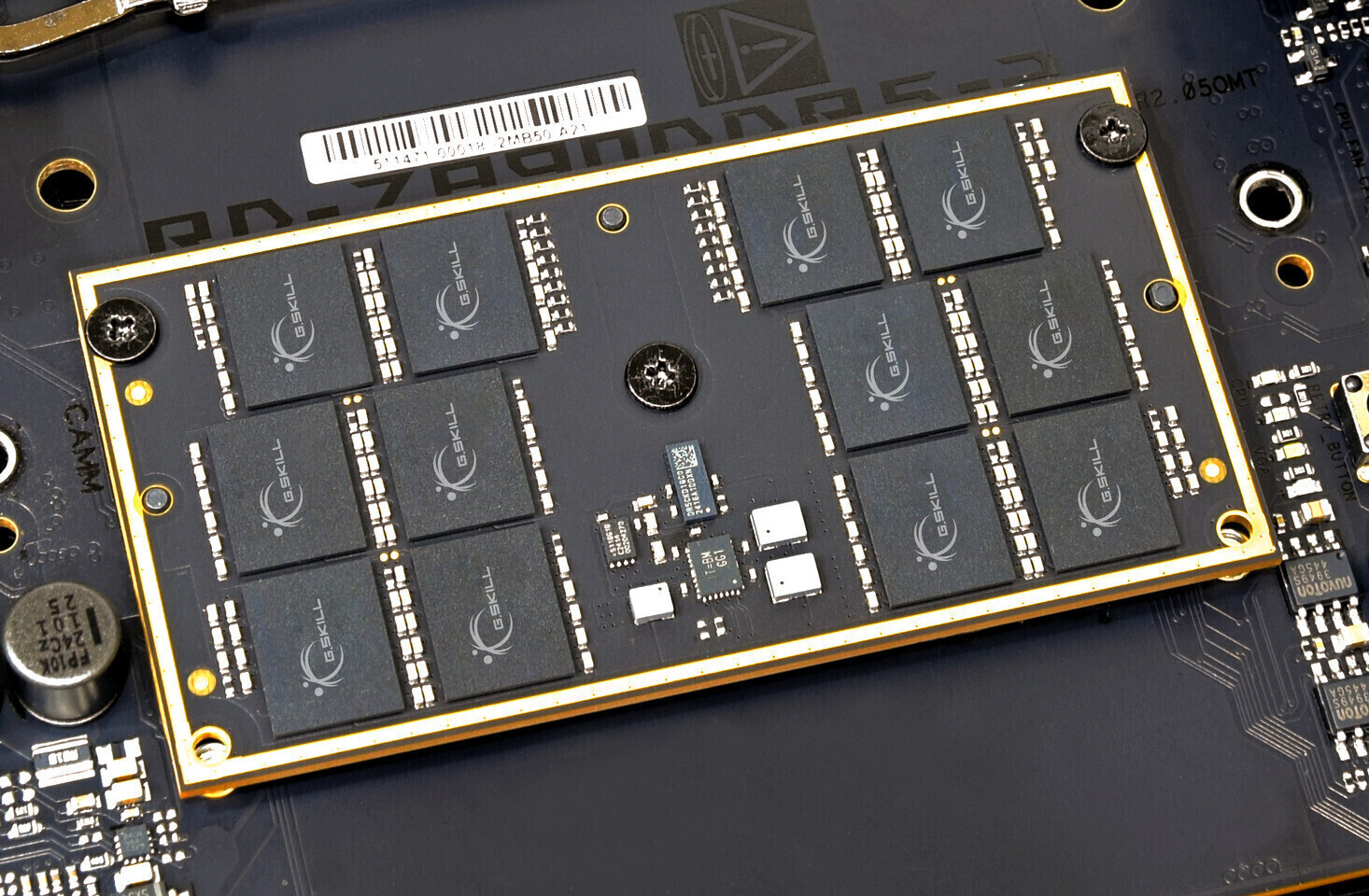

在外界关注的性能指标方面,目前披露的信息显示 DDR6 的目标起步传输速率为 8,800 MT/s,并规划向上扩展至 17,600 MT/s,几乎相当于将现有 DDR5 的速度上限再翻一番。这一大幅提速的核心在于 DDR6 采用 4×24 位子通道架构,需要在信号完整性上引入全新的设计思路。与之相比,当前 DDR5 仍沿用 2×32 位子通道结构,两代标准在通道划分上的差异将对控制器设计、布线与 PCB 层数提出新的要求。

在传统 DIMM 模组在高频下遭遇物理极限的背景下,业界普遍将希望寄托在 CAMM2 技术之上,以缓解高速信号在空间、走线与接口形态上的多重瓶颈。目前迹象表明,服务器平台有望率先导入 DDR6,随后在产能爬坡后逐步下探到高端笔电平台,桌面消费级产品则可能稍晚一步跟进。

从时间表来看,去年业内传出的说法是 DDR6 将在 2027 年“推出”,而最新判断更倾向于将 2027 年视为重点客户验证阶段,真正面向市场的大规模商用则预计在 2028 年实现。与此同时,随着新一代服务器出货和 DDR5 的整体应用渗透率在去年已达到约 80%,并有望在今年进一步攀升至 90% 左右,DDR4 在产业链中的角色正逐渐被视作“待退出”一代。这不仅为新标准预留了更充足的市场空间,也有助于释放晶圆厂的产能,用于后续 DDR6 芯片与模组的大规模生产。